市场对更高性能、更小尺寸、更低能耗的需求从不止步,然而,随着摩尔定律放缓和先进工艺成本攀升,仅靠制程迭代带来的性能增益有限,需要系统级的优化。在这种需求的推动下,集成电路封装技术也在不断进步,为了满足多样化的应用需求,系统级封装(SiP)和FCBGA两种封装形式应运而生,并迅速成为了电子制造业中的热门选择,为电子产品的设计和制造提供更灵活、更高效的解决方案。SiP实现了高度集成的设计,有效降低了芯片的整体体积,提升了系统性能。FCBGA采用了倒装焊接技术,使得连接更短、更紧凑,从而提高了信号传输速率和可靠性。

因应市场需求,年产能亿颗的摩尔精英无锡SiP先进封测中心于2022年正式量产,为客户提供系统级封装(SiP)从设计到量产的完整解决方案,同时与一线封装基板厂深度合作,提供灵活高效的Flip-chip封装解决方案(FCCSP/FCBGA工程批和量产)。无锡SiP先进封测中心测试车间配置数十套以自主机台为基础的CP/FT测试产能,目前已为20家客户50余款芯片产品完成工程开发和数亿颗芯片的量产测试。

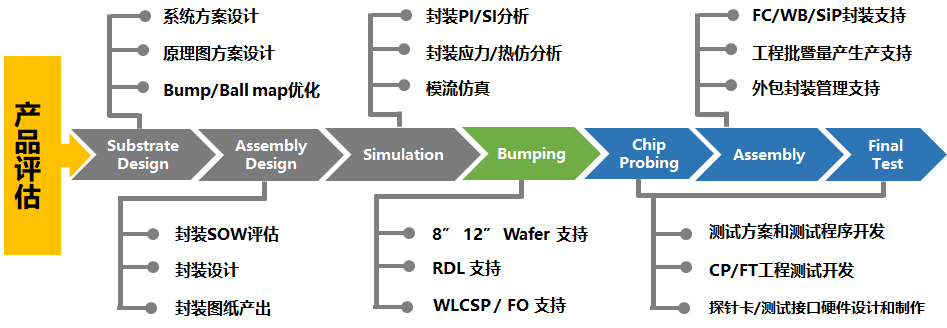

摩尔精英封测协同解决方案

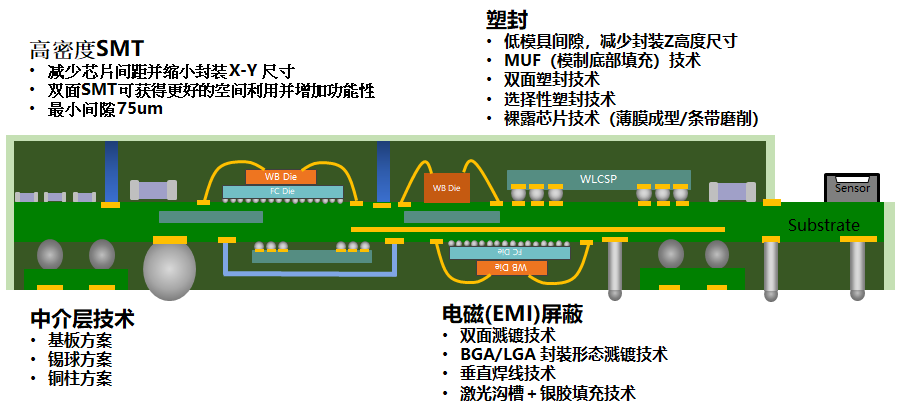

系统级封装SiP

系统级封装SiP

Flip-chip倒装封装

Flip-chip倒装封装

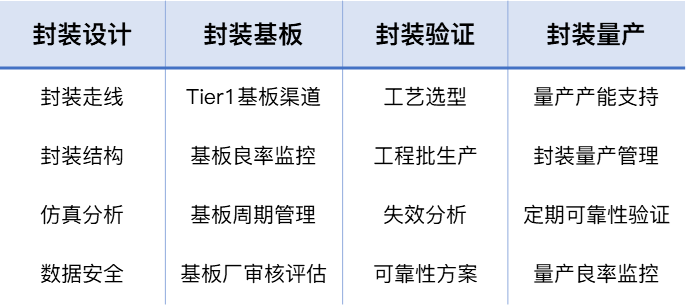

技术能力

技术能力

| SiP | Flip-chip |

| -支持Hybrid WB+FC/package in 多芯片/叠die SiP; -支持高密度SMT封装, Component to die 50um -支持双面BGA SiP封装,最小尺寸 4.1mm x 6.2mm -业界首创三轴立体封装技术 3mm x 2mm -封装级TMV技术开发,最小0.2mm Bump Pitch -EMI shielding 技术,屏蔽能力>45db -POP/PIP/CPO、Difem 滤波器封装技术 |

-支持7nm工艺芯片封装及5nm工艺封装开发; -支持FCCSP封装类型下最薄100um芯片厚度; -支持FCBGA封装类型下最薄400um芯片厚度 -支持最大65*65mm尺寸封装及77.5×77.5封装尺寸开发 -支持最小80um Bump Pitch; -支持高质量、高良率、高性价比的1-16层基板设计、验证和采购; |

基板资源

摩尔精英与一线封装基板大厂深度合作,支持最高6~16层基板的生产,为客户提供打样到量产产能保障。

| 位置 | PKG Size | 层数 | 交期范围(周) |

| 中国台湾 | 19*19~65*65 | 6L~16L | 6~14 |

| 中国台湾 | 23*23~77.5*77.5 | 6L~16L | 8~14 |

| 苏州 | 33*33~60*60 | 8L~10L | 14~21 |

| 上海 | 15*15~30*30 | 6L~10L | 6~8 |

| 南京 | 3*3-20*20 | 1L~8L | 3~10 |

成功案例

| 项目类型 | 交付描述 |

| DPU芯片封装 | 1、28nm IP定制、芯片设计、流片、封装、测试; 2、HSFCBGA 基板设计、仿真、采购,封装验证及生产; 3、ESD高防护要求,高良率要求; |

| IoT三芯合封 | 1、FCBGA 基板设计、仿真、采购,封装验证及生产; 2、多芯合封,平整度及散热胶均匀度达95%; 3、首次验证通过良率达99%,目前已量产; |

| 12层通孔 基板设计 |

1、天线内埋基板,Top to Bottom通孔,Laser Via叠加; 2、国内首例封装工艺; |

| 77.5*77.5 大尺寸封装 |

1、顺利解决封装后Coplanarity要求及多bump count产生的non-wet issue问题; 2、高质量、高良率、高性价比的16层基板支持,顺利保证客户量产; |

| 2.5D封装 | 1、四颗HBM芯片叠封,外加GPU芯片合封; 2、设计两道通道散热盖,缩小尺寸至21mm*21mm; |

| 射频芯片 散热屏蔽 |

1、考虑成本及尺寸限制,利用散热盖对RF芯片进行屏蔽; 2、成本更优、屏蔽效果更佳; |

- 某客户感光SiP芯片顺利量产累计出货已达1.5KK

- 某客户通讯控制SiP芯片顺利量产,累计出货已达500K

- 某客户电动车控制SiP芯片顺利完成工程试样,并且一次性通过测试验证

- 某客户高可靠应用SiP芯片顺利完成工程样品并验证通过

- 某客户射频类SiP芯片顺利完成工程样品并验证通过

如您有需求请扫码联系我们

如您有需求请扫码联系我们

封测基地和客户活动

自运营以来,摩尔精英无锡SiP先进封测中心已通过ISO9001:2015国际质量管理体系标准认证和QC080000认证;同时正积极筹备IATF16949认证,持续加大汽车芯片解决方案研发投入和产能布局。为了让客户更加深入了解工厂运营,我们组织了客户开放日、Flip-chip封装研讨会、SiP技术研讨会等活动,全方位服务客户封装投产和技术支持的需求。

关于摩尔精英