一、两款由学生设计的CPU:摩尔精英芯片设计科研平台,助力高校流片成功mlk点亮

一、两款由学生设计的CPU:摩尔精英芯片设计科研平台,助力高校流片成功mlk点亮

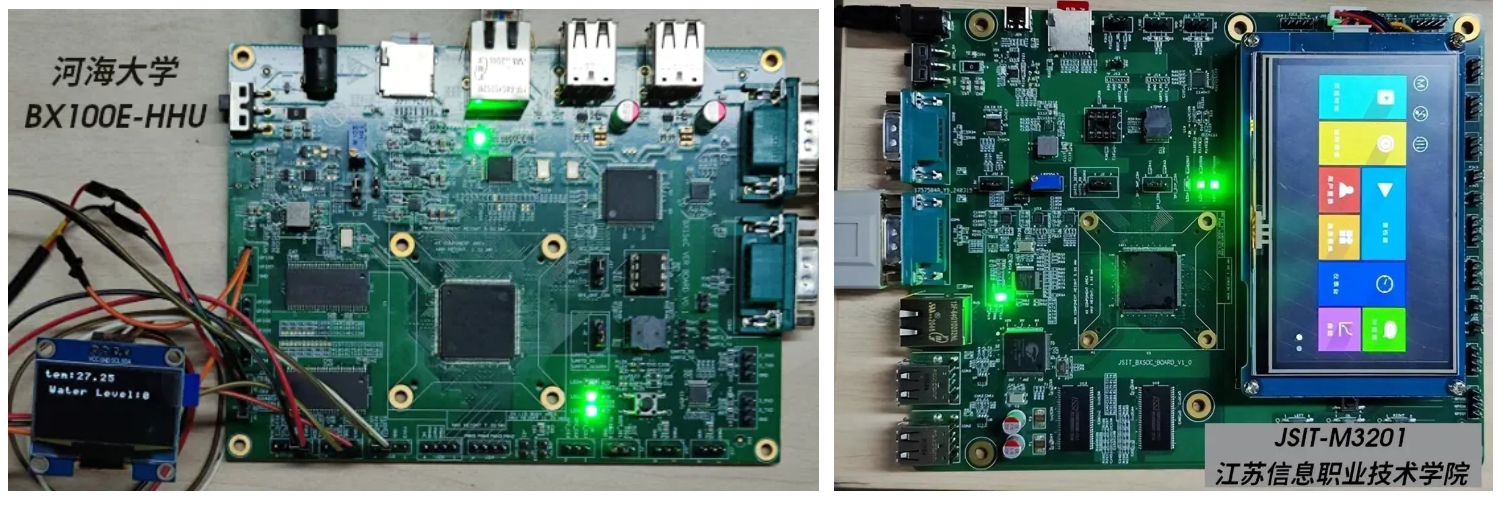

我们先来看两款由大学生设计的CPU,左边是河海大学的“河海智慧水利1号芯”BX100E-HHU,右边是江苏信息职业技术学院的“苏信一号”JSIT-M3201:

“河海智慧水利1号芯”BX100E-HHU于2023年8月19日发布,“苏信一号”JSIT-M3201则于近日流片成功。这两颗CPU的相继诞生,标志着CPU设计技术已经从科研机构和芯片企业下沉到了211大学乃至高职学院。

“河海智慧水利1号芯”BX100E-HHU于2023年8月19日发布,“苏信一号”JSIT-M3201则于近日流片成功。这两颗CPU的相继诞生,标志着CPU设计技术已经从科研机构和芯片企业下沉到了211大学乃至高职学院。

这两款CPU都属于SoC,它们都基于龙芯开源的OpenLA1000处理器核,LoongArch32 Reduced指令集架构,使用180nm工艺流片,都集成了SDRAM、SDIO、MAC、SPI、I2C、UART、PWM、GPIO等一系列丰富的外设接口。它们都拥有出色的运算能力和低功耗特性,平均功耗≤0.5W。

BX100E-HHU计划应用于水利、交通及能源等重点行业的嵌入式、物联网以及智能控制等领域的实际工作中。JSIT-M3201则针对车载应用进行了优化,预计将用于车载中控电脑并提供影音播放功能。

两颗CPU都已经成功点亮并启动系统。下面分别是两款CPU和配套的工程板,江苏信息职业技术学院的主板和软件设计得更加完善,不但搭配了彩色屏幕,还启动了图形化的操作系统。

二、摩尔精英做了啥

二、摩尔精英做了啥

两颗芯片均借助摩尔精英芯片设计产教科研协同创新平台(下简称芯片设计科研平台),完成了数字后端设计,并通过摩尔精英的流片专业服务及基于自有工厂的封装服务,完成了芯片的研制任务,成功应用在高校特定领域。

集成电路产业链环节多,分工精细,科研项目对产业链资源的配套整合依赖较大,是否能迅速及时地匹配恰当的产业资源,对项目的成功与否起了关键作用。

以集成电路设计项目为例,需要涉及到芯片的高性能服务器集群和网络架构搭建,数字或模拟芯片设计的EDA环境的配置,电路设计、IP采购、MPW流片、快速封装和测试等产业链环节,涉及到十几个不同的工种相互间的流畅配合,根据芯片种类和工艺的不同,还需要无缝对接到各大晶圆代工厂、封装测试厂以及IP供应商的账号开立、技术资料的获取和下载、技术问题的讨论和支持、财务支付款等。高校老师经常因此顾此失彼,心力交瘁,造成项目的延误甚至失败。

摩尔精英长期从事高校集成电路产教融合创新事业,经过实地调研和实际项目落地,发现高校通常没有完善的芯片设计研发环境、芯片前后端设计流程、流片封装测试等供应链体系,导致芯片设计科研项目无法有效开展。摩尔精英芯片设计科研平台致力于帮助高校解决科研项目与人才培养最后一公里的问题,以流片为标准培养IC人才,让高校没有难做的芯片!

对于已经建立集成电路设计科研平台的高校,摩尔精英借助IT/CAD事业部多年为芯片设计企业搭建EDA高性能研发集群的经验,可升级现有平台芯片设计软件及芯片设计流程环境,数据安全管理,提供自研芯片设计管理软件支持,芯片设计课程输入及工程技能实训,芯片设计服务及芯片设计咨询与一站式供应链服务(MPW+快封)。

对于筹建集成电路设计科研平台的高校,摩尔精英可提供IC设计行业专属的IT解决方案,一站式搭建芯片设计软硬件环境,包括硬件设备、芯片设计及集群管理软件部署、工艺库及IP核部署等。

对于暂未建立集成电路设计科研平台的高校,摩尔精英将于5月官宣“芯片科研云大学计划”,以个人消费级价格为教师及科研团队提供芯片设计科研平台账号租赁,低成本高效开展芯片设计科研项目。

芯片设计科研平台 功能概述

芯片设计科研平台 网络拓扑

芯片设计科研平台 芯片设计流程

芯片设计科研平台 芯片应用开发

三、中科龙芯做了啥

这两颗由中科龙芯的“百芯计划”提供CPU的IP核与设计工具。

百芯计划的主要内容是:计划在5至10年内,在全国范围选择百所高校,以校企合作的模式,共建百个“芯片联合实验室”。联合实验室将基于龙芯高校计划免费提供的IP,可联合第三方共同研发实用型的自主芯片,并形成产业化应用。

百芯计划开源了两款升级版的CPU核心,分别是OpenLA500和OpenLA1000。这两款CPU核心都源自龙芯产品级的成熟设计,并允许学校联合其他企业用于产品研发。除了两款CPU核,龙芯还提供了其它各种IP核,可以用这些IP核整合出商业级的产品。

四、关于摩尔精英芯片设计科研平台

摩尔精英芯片设计产教科研协同创新平台(简称芯片设计科研平台):以摩尔实训云为基础结合摩尔芯片设计团队与IT/CAD能力,为高校提供集群化的芯片设计本地部署平台,支持不同工作室学生老师进行芯片设计科研项目,并配套PDK工艺库与技术支持、IP资源库与技术支持、EDA工具库与技术支持、IT基础架构与技术支持、CAD技术支持等多种技术支持平台/服务,协助高校更好地完成芯片设计类科研项目。同时,结合摩尔精英自有供应链平台为高校提供从芯片设计到流片到封装测试一体化服务。

需求提交/联系我们

关于摩尔精英